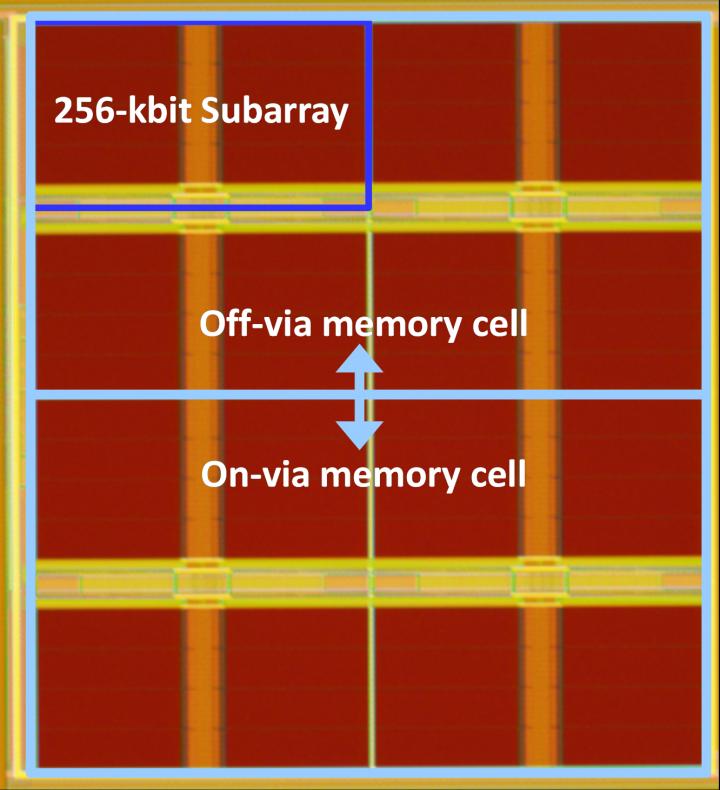

制作了2mbit MRAM测试芯片,用于在VLSI通孔上直接验证所开发的MTJ地层技术。信贷Yoichi大岛渚

日本东北大学(Tohoku University)的研究人员成功开发了一种技术,可以直接将磁隧道结(MTJ)堆叠在垂直互连接入点(via)上,而不会导致其电/磁特性的恶化,这在世界上是首次。通孔在集成电路设计中是一个小的开口,允许半导体器件的不同层之间的导电连接。

这一新发现对于减小自旋传递转矩磁随机存取存储器(STT-MRAM)的芯片面积,使其商业化更具实际意义。

由创新集成电子系统中心(CIES)主任Tetsuo Endoh教授领导的团队专注于减少STT-MRAMs的存储单元面积,以降低制造成本,使其与传统半导体存储器(如动态随机存取存储器(DRAM))竞争。

由于MTJ使用磁性,所以MTJ和下电极之间的表面质量很重要。如果表面不光滑,MTJ的电磁特性将会退化。由于这个原因,在STT-MRAMs的通孔上直接放置一个MTJ一直被避免到现在,尽管它增加了存储单元的大小。

恩多的团队已经通过开发一种特殊的抛光工艺技术来解决这个问题,以防止MTJ和它的下电极之间的任何干扰。通过单mtj测试芯片的实验,验证了该技术的有效性。

为了进一步测试这一开发的成功,集成了新技术的2兆STT-MRAM测试芯片已经被设计出来,以验证集成电路所需的空间——这包括超过100万mtj。

“与标准STT-MRAM相比,该测试芯片的内存比特率不仅提高了70%,而且内存单元面积减少了30%,”Endoh说。这对于减小MRAM的芯片面积是非常有效的。”

CIES开发集成电子系统的材料、工艺、电路和测试技术。该中心的主要重点是为一个更加节能的社会开发高性能、低功耗的技术。

这项研究的结果于2016年5月16日在法国举行的IEEE国际记忆研讨会上发表。

这项研究得到了CIES联盟项目的支持。

了下:工业自动化