数字时钟随处可见。事实上,这里的钟太多了。如果你用频谱分析仪做一个快速扫描,那么除了你可能期望看到的频率——地方电视和广播电台,手机和WiFi信号——你会发现各种各样的其他虚假信号来自你的房子/办公室/口袋里的设备。大多数产品都有一些数字元素,这意味着一个时钟设备。它可能是一个微控制器或FPGA,但它也可能与本地的其他芯片或它插入的其他设备通信。在过去你会发现微处理器与陌生的时钟频率,仅仅是因为它可以被划分到一个方便的串行通信波特率如7.3728 mhz晶体——如果你足够除以2乘以你可以获得很多便利的波特率从115200年开始下降。

现在有一个锁相环(PLL)的时钟无处不在,以及可编程分频器,所以我们不受这样粗糙的时钟选择的限制。我们可以为微控制器或FPGA选择一个时钟,使用锁相环产生更高的频率,可编程分频器产生更低的频率。甚至有一些时钟芯片可以从你的输入时钟中产生几乎任何你想要的频率。不过,所有这些时钟都可能造成问题。你现在在电路板上有小型发射器,因为时钟边缘相当快,它们会产生大量的谐波,主要是奇谐波,也就是第三次,第五次,第七次谐波等等。如果你有任何敏感的模拟电路附近或PCB,那么你可能有一个问题。您还可能无法通过EMC遵从性测试。

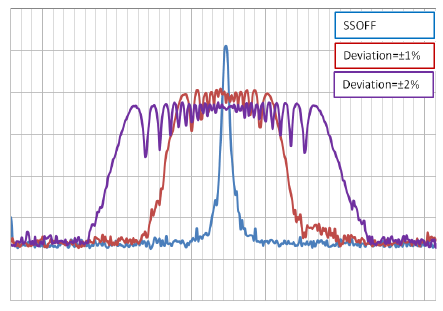

减少数字时钟干扰的一种方法是使用扩频时钟。这包括产生一个时钟,它的频率围绕中心,即所需的频率略有变化。它具有“扩展”时钟频谱的作用。ON Semiconductor AND9015的应用说明说明了这种效果:

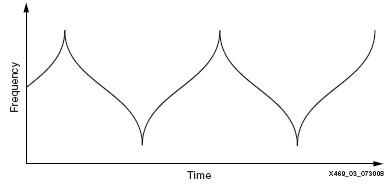

扩频关闭后,在时钟的频率上有一个主要的峰值。当扩频打开时,时钟发出的频率就会扩展,在这种情况下,以时钟频率为中心,所以平均频率保持不变。偏移量(调制深度)影响峰值杂散信号电平,但调制速率和调制轮廓也影响得到的频谱。调制速率通常在音频范围内。一个逻辑调制轮廓是线性的,即频率从频率调制的一个极端线性地改变到另一个极端,并使用三角调制轮廓以线性方式返回。然而,好时的Kiss或利盟调制方案进一步减少峰值排放。Hershe 's Kiss调制的频率与时间关系图如下所示,来自Xilinx应用程序说明XAPP469。

其他调制方案也可以使用,如正弦调制和鱼翅调制。鱼翅调制是基于指数电容充放电,所以很容易产生,但没有利盟或好时的吻那么有效,尽管比线性调制更好。注意,增加偏移量会产生递减效果。虽然只有0.5%的小偏差就能显著减少峰值排放,但越来越大的偏差对减排的影响却越来越小。这可以在前面的ON Semiconductor图表中看到。

同时,请记住,如果考虑到总辐射能量,实际上并不是在减少排放,只是将其分散开来,这样峰值就会降低。然而,排放法规寻找的是辐射的峰值水平,而不是平均功率或能量,所以扩频时钟确实有助于压缩到允许的水平以下。

由时钟引起的干扰不仅局限于直接时钟,而且也适用于由原始时钟衍生出来的任何时钟。例如,这可以包括外部存储器的地址和数据线。这些线路可能是引起额外辐射的天线,因为它们通常比实际的时钟路由长,而实际的时钟路由通常是相当短和直接的。

如果您的微控制器或FPGA没有扩频时钟选项,您可以通过使用许多扩频时钟生成芯片之一轻松添加它。它们通常采用一个输入时钟并产生一个扩频输出时钟。最简单的将产生1:1的输出与输入时钟比,即频率不变。更复杂的设备将提供可编程峰值偏差和多个时钟输出与各种可编程乘法器/分法器使用内部锁相环。

![]()

了下:•专家见解,技术+产品,单片机的技巧