Cadence Design Systems宣布Innovus实施系统用于先进的16/14/10nm制程和已建立的制程节点的片上系统(SoC)开发。结合并行架构和专有优化技术,Innovus提供了10%到20%的更好的功率、性能和面积(PPA),并高达10倍的全流加速和容量增益。并行数字实现结合了多线程和分布式网络处理,允许作业分布在网络上的多台机器上,并且适用于包含1000万个或更多实例的设计块。

Cadence产品管理团队总监Rod Metcalfe表示:“如今,SoC设计中存在两大对立的目标。“设计人员被要求以更快的速度制造更多芯片,但为了满足当今的功率性能区(PPA)需求,他们在电路上花费了太多的时间。传统的系统解决了周转时间或PPA问题。Innovus。”

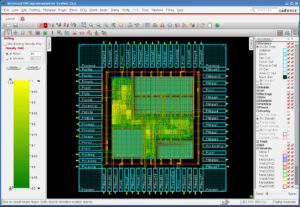

Innovus整合了公司基于GigaPlace求解器的布局技术,该技术是由松弛驱动和拓扑/引脚访问/颜色感知的,实现了最佳的管道布局、电缆长度、利用率和PPA,并为优化提供了最佳起点。根据梅特卡夫的说法,GigaPlace考虑了电路的许多不同方面,包括时间、层分配、槽的放置,因此得到了更好的放置质量。其他功能包括:先进的时间和功率驱动优化,是多线程和层感知,减少动态和泄漏功率的最佳性能;并行时钟和数据路径优化,包括自动混合h树生成,提高跨角变异性,在降低功耗的情况下实现最大性能;松弛驱动的路由与跟踪感知的时间优化,解决早期信号完整性和改善后路由相关性;采用全流多目标技术,实现电物理并行优化,避免局部最优,得到最全局最优的PPA。

该系统提供跨综合,实现和签收工具的常见用户界面(UI),以及与Tempus时序源和Quantus QRC提取的数据模型和API集成。这些系统一起允许快速,准确,10nm就绪的源。可视化和报告工具有助于增强的调试,根本原因分析和指标驱动的设计流管理。

您可以找到其他Innovus资源,包括视频,数据表,白皮书,早期客户推荐等等在这里。

节奏设计系统

www.cadence.com.

帖子复杂SoC设计的实现系统首先出现了模拟集成电路提示.

了下:技术+产品