大多数电压稳压器仍然使用离散的解决方案,如SO8-FL 5 x 6 mm2包。随着硅技术和封装的进步,MOSFET可以实现小于10nS的开关转换,相当于di/dt大于1A/nS。新型PowerPhase封装通过最小化封装寄生电感实现更快的开关。使用SO8-FL的旧解决方案效率较低,而新的集成封装,布局要求不那么关键,开关频率受到封装寄生电感的限制。本应用说明指出了功率MOSFET在现代高功率密度电压调节器中的一些应用问题。会议将讨论以下主题:

计划建设

- SO8-FL vs PowerPhase

PowerPhase建议

- 动力循环

- 解耦电容的位置

- 布局

- 探索

PowerPhase应用程序问题

- 阶段节点过度

- 低侧Off-State Gate Bounce

- 高侧开尔文连接

- 低侧栅电阻器

- 不同的高端驱动程序连接

包

SO8-FL和PowerPhase封装的结构差异

SO8-FL和PowerPhase封装是5 x 6 mm2。传统的SO8-FL封装有MOSFET的漏极连接到引线fig1框架和源夹连接(图1)。PowerPhase是半桥配置的双模设备。低侧模翻转,源附在引线框架上,高侧模有开尔文源连接(图2)。

在同步降压变换器中,两个MOSFET器件形成半桥结构。SO-8FL溶液(图3)具有两个互连夹寄生fig3电感的最小1h总封装电感。PowerPhase解决方案的电感减少了一半(图4)。PowerPhase还通过利用高侧开尔文连接来减少开关时间,该连接绕过了驱动器环路[1]的夹电感。

建议

降低电力的循环

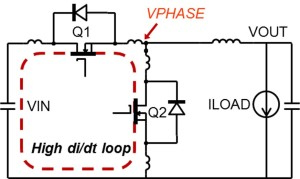

由于开尔文连接,漏极电流的过渡速度di/dt增加了。相节点电压超调可能非常严重。在高侧开关过渡期间,电流由去耦电容提供。寄生功率回路电感和低侧输出电容(图5)形成谐振电路,引起相节点环和功率损耗。功率回路是大电流di/dt路径(图6)。总功率回路电感由图5中的封装和输入去耦电容之间的布局电感组成。一种降低振铃能量的方法是尽量减小功率回路的电感。

输入去耦电容布置

由于在PowerPhase足迹[2]上的输入电压引脚和接地引脚非常接近,可以通过在引脚4旁边放置去耦电容来实现最小的功率回路电感(图7中的PL1)。其次最好的放置方式是直接放置在正下方(图7中的PL3)或与PowerPhase放置在一起(图7中的PL2)。这两种放置方式都利用了内部PCB层来消除磁场。在典型的40 mil 4层板厚(图7第2层为接地面)上,放置PL1的功率回路电感约为1.3nH(包括封装贡献)。放置PL2和PL3近似为1.4nH。

推荐PowerPhase布局

图8所示的推荐布局的目标是将大电流路径与信号路径分开。在图9中,红色阴影的高电流路径由寄生电感产生感应噪声电压。通过将输入去耦电容和栅极信号放置在相反的两侧,可以使它们的干扰最小化。如果可能的话,将驱动器IC放置在G2引脚附近,以实现最小的低侧栅反弹。热通道是最有效的降低结温度时,当放置在包。总结了重要的布局规则:

- 最小化功率回路面积

- 输入去耦电容布置

- 使用S1引脚作为高端驱动器返回

- 足迹下面有热通道

- 最小化控制器信号和功率回路重叠

探索

在评估过电压风险时,需要采用低电感探测技术。在图10a中,红色恒星表示VGS和VDS测量的推荐探头位置。探测的一个常见错误是指向错误的接地点(黑点)。例如,将所有探头参考到输入电容接地将增加LPCB·di/dt噪声到测量中。

在不同的地面基准上捕获了两个低侧门电路波形VGS。有一个主要的不同,在最初的门反弹(图10b)。正确探测PowerPhase VGS, LGATE,初始栅极反弹负由于板电感di/dt。LGATE2波形是带有寄生电感噪声的真VGS失真。LGATE2波形类似于带源夹电感的封装。高栅极电感从布线将最小化最初的负栅极反弹。

应用程序问题

这种快速切换的PowerPhase包需要最佳的布局实践。在具有离散mosfet的多相电压调节器中,空间和方向的约束会产生次优布局设计。

阶段节点过度

相节点电压不应超过低侧MOSFET漏源极击穿电压。探测相节点电压应尽可能接近低侧漏源极(参见图10a)。相节点振铃是由总功率回路电感和低侧输出电容在谐振槽中形成的低侧反向恢复fig12电流引起的(图11)。可以增加缓冲器或高侧升压电阻,以减少相节点超调。

低侧Off-State Gate Bounce

大门反弹有两个原因。来自相位节点dv/dt的CGD电流注入,来自源电感di/dt的谐振槽环电流注入。在高侧开启上升相节点电压导致dv/dt穿过低侧MOSFET的CGD时,电流流过CGD并在栅极电阻和CGS之间分裂(图12a)。dv/dt的最坏情况将是一个大的栅极电阻,导致大多数CGS电流充电。由dv/dt得到的感应栅极电压如下图所示:

低侧源,板电感和栅极电容,CGS,形成一个谐振槽,并与反向恢复电流产生另一个栅极反弹贡献(图12b)。寄生电感上的第一个正峰值电压导致低侧栅源电压变得更负(图11)。下面的负峰值电压导致低侧栅源极电压变为正,并在低侧MOSFET上实现电位转换。在di/dt的最坏情况下Rg小的条件下,能量在源、LS、板电感、LPCB之间振荡,能量在CGS之间传递,阻尼小。长栅极路由(高栅极电感,LG)在较低频率产生额外的栅极振荡。

S1引脚-高侧开尔文连接

对于高边MOSFET,一个专用的栅极驱动返回引脚(S1引脚)增加了开关速度(图13)和效率。在离散解决方案中,这种开尔文源实现需要达到最高的效率。这些低电感封装极大地增加了di/dt fig15过渡。在没有改进布局的情况下,提高开关速度的风险是增加电压超调和电位击穿。

增加1Ω低侧栅电阻

由于高侧开尔文连接,非常快速的转换可能导致穿透。随着速度的增加和MOSFET电容的降低,同步MOSFET非常容易受到高di/dt注入噪声的影响。一个小的低侧栅极电阻可以增加低侧MOSFET栅极驱动环路的阻尼。这个额外的小栅极电阻对同步低侧MOSFET的开关损耗影响很小,但di/dt击穿抗扰度却有巨大的增加(图14)。

在使用分立mosfet的多相控制器中,门路由电感(LG)和板电感(LPCB)是不可避免的(图15)。在高侧MOSFET导通期间,漏极电流di/dt将相对于驱动IC接地基准产生接地反弹。最坏的栅极反弹会发生在距离驱动器IC最远的相位。地反弹信号滤波可以通过增加总栅极电阻(RG)来增加。

不同的高端驱动程序连接

在PowerPhase包上有两个相节点连接,S1和SW。S1和SW引脚内部通过金属夹连接。虽然夹子的电阻只有0.3mΩ,但电感是0.5nH。在接通和关断过渡期间,漏极电流di/dt (>1A/ns)可以在电极上感应到几伏电压。这些诱导电压减缓了开关转换,导致效率降低,但产生较小的相位节点振铃幅度。用户通过从SW引脚连接高端驱动信号来优先简化路由是很常见的。图16显示了四种不同的可能的高端驱动器连接。表1总结了它们对性能的影响。在图17中,绿色条纹区域表示高侧驱动开启路径,红色阴影区域表示关闭路径。图17a中推荐的高侧驱动器连接绕过了内部夹阻抗。

`

![]()

了下:电力电子的技巧