2015年12月7日至9日,在美国华盛顿希尔顿酒店举行的第61届IEEE国际电子器件会议(IEDM)上,以物联网为主题的新型半导体器件将成为热门话题。IEDM被认为是微型和纳米电子学领域的科学家和工程师的主要论坛,今年的IEDM包括几个面向满足低功率电子需求的节能设备的演讲。

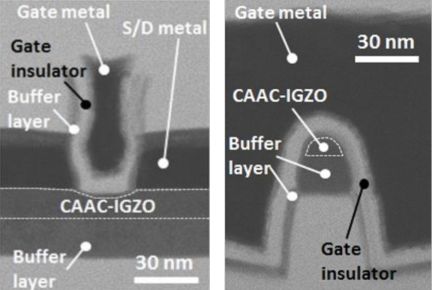

其中一篇介绍了高频、低泄漏的铟镓锌氧化物(IGZO)晶体管。来自日本半导体能源实验室的一个团队将描述他们如何制造出具有< 0.1 pA的超低关态电流,但截止频率超过10 GHz的20纳米门-全方位mosfet。晶体管由IGZO薄膜制成。它们是使用自对准过程构建的,消除了从栅极到源极和漏极的重叠,使通道不受短通道影响,否则会降低性能。集成在DRAM存储单元中以展示其性能,其极低的关断电流允许在125°C下数据保留超过10天。本文,20-NM节点沟槽 - 栅极 - 自对准晶体In-Ga-Zn-氧化物FET,具有高频和低电击电流;是由Daisuke Matsubayashi等,半导体能源实验室有限公司。

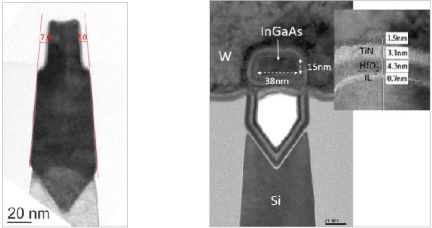

另一篇纸张覆盖硅上的Ingaas纳米线FET。虽然III-V通道对低功耗逻辑器件有益,但是有关其可制造性的问题。在IEDM,由IMEC领导的团队将讨论基门,高性能Ingaas纳米线MOSFET,内置于300毫米硅晶圆上。它们具有高跨导(GM = 2,200),尽管具有晶格 - 不匹配的基板,但InGaAs通道材料保持其高载流速。本文,采用替代Fin RMG Flow的栅极-全面InGaAs纳米线场效应晶体管,在50nm Lg下峰值跨导为2200 μS/μm,是N. Waldron等,IMEC / ASM。

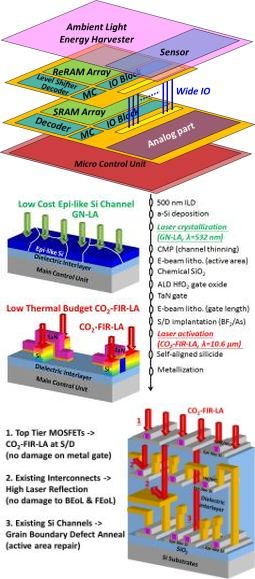

IEDM的重点是将芯片电子和传感器集成在同一基片上,使物联网传感器可以超级便宜。在这方面,一个由台湾国家纳米设备实验室领导的团队研究了一种改进单片3D芯片设计的方法。构建3D电路的通常方法是将单独的芯片堆叠起来,并用硅通孔(tsv)将它们电连接起来。但是tsv有明显的缺点,包括相对狭窄的I/O带宽。单片3D集成电路没有tsv,但其结构需要热退火,这可能会损坏晶体管——3D设备中的每一层都必须退火,以消除其晶体硅结构中的应力,并激活植入其中的掺杂剂。

研究人员通过使用CO来解决了这个问题2远红外激光在400°C选择性脉冲退火特定区域的硅(源漏区)。他们使用这种技术构建了一个小于40纳米的单片集成电路,其中包含各种不同的功能——逻辑、SRAM、RRAM、传感和模拟放大器以及气体传感器。没有设备退化的报告,研究人员表示,他们的技术适合制造物联网所需的低功耗、低成本、小占地面积和异构集成设备。

本文,低成本和无TSV单片3D-IC,具有逻辑,内存和传感器类别电路的异构整合,用于物联网,是Tsung-Ta Wu等,国家纳米设备实验室/国家青花大学。

有关注册和其他信息,请访问IEDM 2015主页www.ieee-iedm.org.或者联系Phyllis Mahoney,会议经理电话(301)527-0900 ext。2。

帖子国际电子设备会议

看看模拟电路的新想法第一次出现在模拟IC提示。

![]()

提交:模拟IC提示